Hindawi Publishing Corporation Advances in Condensed Matter Physics Volume 2014, Article ID 632785, 7 pages http://dx.doi.org/10.1155/2014/632785

## Research Article

# Fowler-Nordheim Tunneling Characterization on Poly1-Poly2 Capacitors for the Implementation of Analog Memories in CMOS 0.5 $\mu$ m Technology

Enrique J. Tinajero-Perez, <sup>1</sup> Jesus Ezequiel Molinar-Solis, <sup>1</sup> Rodolfo Z. Garcia-Lozano, <sup>1</sup> Pedro Rosales-Quintero, <sup>2</sup> Jose M. Rocha-Perez, <sup>2</sup> Alejandro Diaz-Sanchez, <sup>2</sup> and Arturo Morales-Acevedo <sup>3</sup>

Correspondence should be addressed to Jesus Ezequiel Molinar-Solis; molinar@gmail.com

Received 28 October 2013; Accepted 7 January 2014; Published 23 February 2014

Academic Editor: Rodrigo Picos

Copyright © 2014 Enrique J. Tinajero-Perez et al. This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

The experimental results of the Fowler-Nordheim characterization using poly1-poly2 capacitors on CMOS ON Semi  $0.5\,\mu\mathrm{m}$  technology are presented. This characterization allows the development, design, and characterization of a new current-mode analog nonvolatile memory. Experimental results of the memory cell architecture are presented and demonstrate the usefulness of the proposed architecture.

#### 1. Introduction

For decades, the floating gate MOS transistors (FG-MOS) have been used as an important element for analog and digital circuit design. Over the years, a wide spectrum of floating gate devices has been proposed for analog applications. Some of them are related to the development of analog nonvolatile memories [1], where the storage of charge in a floating gate (FG) cell is later used as information in voltage-mode or current-mode. This kind of devices is very useful for trimming in analog circuits and information storage for artificial neural networks. Several methods have been used for injecting or removing charge onto a floating gate: the hot electron injection (HEI), Fowler-Nordheim tunneling (F-N) [2], and UV conductances [3]. Over the time, many analog nonvolatile cells have been proposed; Fujita and Amemiya [4] present a structure that has two floating gates connected through a high resistance  $\sim$ 1 G $\Omega$ . Though it is a compact cell, it is not achievable in standard CMOS processes, since the integration of such high resistances is not possible.

In the paper [5], Harrison et al. present an on-chip nonvolatile analog memory array. The design uses NMOS transistors with N-well layer as drain in order to address high voltages on chip. Thus, this high voltage is used to allow F-N for programming a specific cell in the whole array. However, the design of an NMOS with this feature violates a design rule related to "active to well edge" in standard CMOS technology.

Figueroa Toro [6] proposes a negative feedback floating gate configuration with two transistors, one capacitor and one inverter amplifier. In this case it is necessary to include an on-chip charge pump, which is used to induce the F-N mechanism. Hence, the design area is augmented by the need of special circuitry.

Moreover, Diorio et al. [7] presents a structure with two PMOS transistors. One transistor has a thin gate oxide that tunnels at much lower voltages. The other transistor

<sup>&</sup>lt;sup>1</sup> Centro Universitario Ecatepec, Universidad Autónoma del Estado de México (UAEMex), Laboratorio de Electrónica, José Revueltas 17, Tierra Blanca, 55020 Ecatepec, MEX, Mexico

<sup>&</sup>lt;sup>2</sup> Instituto Nacional de Astrofísica, Óptica y Electrónica INAOE, Luis Enrique Erro 1, 72840 Tonantzintla, PUE, Mexico

<sup>&</sup>lt;sup>3</sup> Centro de Investigación y Estudios Avanzados del I.P.N, Sección de Electrónica del Estado Sólido, Avenida Instituto Politécnico Nacional No. 2508, Col. San Pedro Zacatenco, 07360 Mexico, DF, Mexico

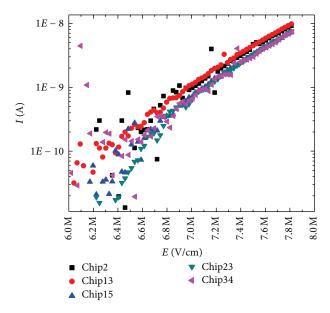

FIGURE 1: Measured tunneling current from five different capacitors *I* versus *E*.

uses high drain voltages to induce the HEI mechanism in order to increase the electron charge onto the floating gate. Nevertheless, the thin oxide layer tends to degrade with the use of the cell. Thus, the lifetime of the cell is reduced notably.

In this paper, the F-N characterization and the design of a current-mode analog nonvolatile memory are presented. The key element avoids the use of internal high voltages devices (>10 V) on-chip for addressing the F-N programming mechanism. The cell design uses a single floating gate, a polylpoly2 injector, and a control gate. Thus, F-N tunneling is used to charge and discharge the floating gate. The sections of this paper are organized as follows: the next section will explain the characterization of the F-N current in polyl-poly2 capacitors. Section 3 gives an overview of the cell design. Section 4 reviews the simulations and the experimental results are presented. Finally, the conclusions are presented in Section 5.

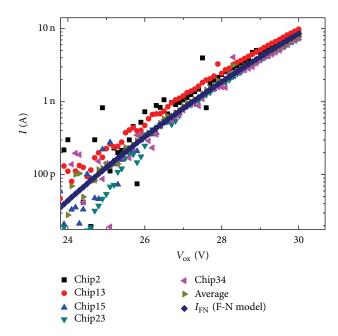

### 2. F-N Characterization on Poly1-Poly2 Capacitors

Depending on the thickness of silicon oxide, there are several electron-transport mechanisms. The F-N tunneling is the dominant mechanism when the oxide thickness is greater than a few tens of nanometers and electrical fields ( $E_{\rm ox}$ ) greater than 6 × 10<sup>6</sup> V/cm [2]. The current density ( $J_{\rm FN}$ ) caused by the F-N tunneling through a SOS (silicon-oxide-silicon) capacitor of area A can be described by the following classical equation:

$$J_{\rm FN} = C_{\rm FN} E_{\rm ox}^2 \exp \left[ -\frac{4}{3} \frac{\sqrt{2m_{\rm ox}^*}}{q\hbar} \frac{(q\phi_B)^{3/2}}{E_{\rm ox}} \right],$$

(1)

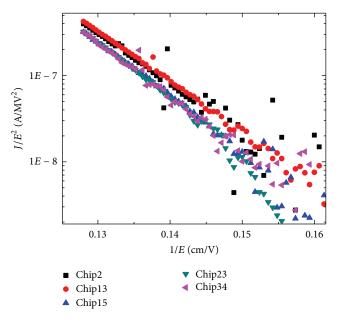

FIGURE 2: F-N plot  $J/E^2$  versus 1/E.

where  $C_{\rm FN}$  is a constant,  $E_{\rm ox}$  is the electrical field,  $m_{\rm ox}^*$  is the effective electron mass in the oxide, q is the electron charge,  $\hbar$  is the normalized Planck constant, and  $\phi_B$  is the barrier height between conductor and isolator layer, in this particular case, highly doped polysilicon. As depicted in Figure 1, the I- $E_{\rm ox}$  curves from 5 capacitors fabricated over 5 different chips are shown. When electrical field is less than 6.3 MV/cm, the current is negligible. Moreover, as electrical field increases, electrical current also increases; this suggests that F-N tunneling could be the dominant mechanism. To prove that the transport mechanism is F-N tunneling, it is necessary plot  $\log (J_{\rm FN}/E_{\rm ox}^2)$  versus  $1/E_{\rm ox}$  to obtain a straight line as shown in Figure 2.

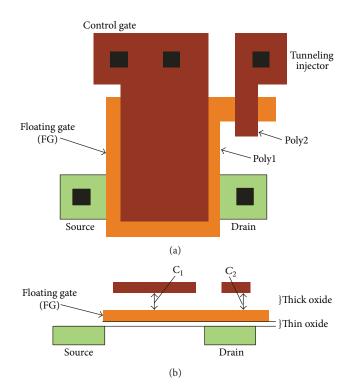

The proposed floating gate transistor has a tunneling injector and a control gate (Figure 3). In this device, considering negligible parasitic capacitances, the floating gate potential  $V_{\rm FG}$  (potential at FG node with respect to substrate) is approximately given by [8]

$$V_{\text{FG}} = \frac{C_1}{C_T} V_C + \frac{C_2}{C_T} V_{\text{tun}},$$

(2)

where  $V_C$  is the control gate voltage through  $C_1$  capacitor;  $V_{\text{tun}}$  is the voltage at the charge injector that couples to the floating gate through capacitor  $C_2$ , and  $C_T$  is the total capacitance of the floating gate.

For this case, the cell is designed with the condition  $C_1 \gg C_2$ ; thus, ratio  $C_1/C_T \approx 1$ . Hence, floating gate potential  $V_{\rm FG}$  is practically defined by control gate potential  $V_{\rm C}$ ; that is,  $V_{\rm FG} \approx V_{\rm C}$ .

The F-N mechanism allows injecting or extracting electrons from the floating gate. As the potential difference between the floating gate and the charge injector is enough to achieve a critical electrical field, a current is established. The

FIGURE 3: Topological design of an FGMOS transistor with a tunneling injector: top view and side view.

current density is theoretically characterized by the Fowler-Nordheim equation [2]:

$$J = \alpha E^2 \exp\left(-\frac{\beta}{E}\right),\tag{3}$$

where J is the current density, E is the electrical field in the oxide, and  $\alpha$  and  $\beta$  are technological constants. For simplicity, we assume that charge injector-floating gate structure is a parallel plate capacitor of area A separated by a distance d. Thus, the electric field in the injector is given by

$$E = \frac{V_{\text{ox}}}{d},\tag{4}$$

where  $V_{\rm ox} = V_{\rm tun} - V_{\rm FG}$ . Considering that current tunneling is achieved through all the charge injector area, we can express (3) as follows:

$$I_{\rm FN} = A\alpha \left(\frac{V_{\rm ox}}{d}\right)^2 \exp\left(-\frac{\beta d}{V_{\rm ox}}\right),$$

(5)

where  $\alpha$  and  $\beta$  are fit parameters which must be extracted experimentally from CMOS technology.

In order to obtain  $\alpha$  and  $\beta$  from experimental data, (5) must be linearized. Therefore, using natural logarithm in both sides, (5) is transformed to

$$\ln\left(\frac{I_{\text{FN}}}{V_{\text{ox}}^2}\right) = \ln\left(\frac{A}{d^2}\alpha\right) - \frac{\beta d}{V_{\text{ox}}}.$$

(6)

FIGURE 4: (a) Capacitor microphotograph. (b) Measuring equipment and testing structure.

This has the linear form

$$y = k - \beta dx,\tag{7}$$

where

$$y = \ln\left(\frac{I_{\rm FN}}{V_{\rm ox}^2}\right), \qquad k = \ln\left(\frac{A}{d^2}\alpha\right), \qquad x = \frac{1}{V_{\rm ox}}.$$

(8)

Thus, through the *I-V* characterization of polyl-poly2 injector,  $\alpha$  and  $\beta$  can be extracted using linear fitting.

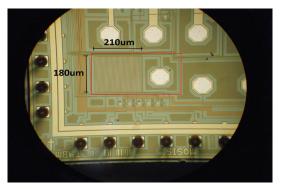

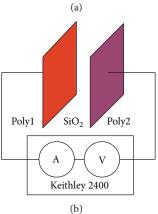

2.1. Parameter Extraction. Several testing polyl-poly2 capacitors were designed and fabricated on CMOS 0.5  $\mu$ m technology; these capacitors have an area  $A=180~\mu$ m  $\times$  210  $\mu$ m and d=38.4 nm (Figure 4). The *I-V* curves from 40 capacitors were obtained using Keithley 2400 sourcemeters. The extracting methodology was accomplished with the arithmetic average of the *I-V* curves. The following values for  $\alpha=86.51\times10^{-12}~\text{A/V}^2$  and  $\beta=150.56~\text{MV/cm}$  were obtained; consequently, the F-N current expression is

$$I_{\text{FN}} = 86.51 \times 10^{-12} \left(\frac{A}{V^2}\right) A \left(\frac{V_{\text{ox}}}{d}\right)^2 \times \exp\left(-\frac{150.56 \times 10^6 \,(\text{V/cm}) \,d}{V_{\text{ox}}}\right). \tag{9}$$

FIGURE 5: Five structures with F-N tunneling current, average curve, and F-N model using technological parameters.

This expression brings a close approximation for the F-N current for a given polyl-poly2 tunneling injector with area A and distance d between plates.

Only five I-V curves from different capacitors are shown for clarity in Figure 5; the average curve and the  $I_{\rm FN}$  model for the capacitors are also shown in the same plot. A good fitting among I-V measurements, average, and the proposed  $I_{\rm FN}$  model can be noticed.

#### 3. Memory Cell Design

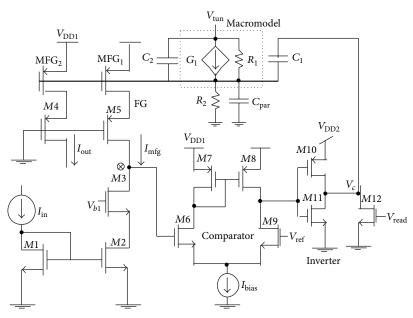

The current-mode analog memory cell proposed in this paper stores charge onto the floating gate of MFG<sub>1</sub> and MFG<sub>2</sub> transistors in order to set a given current  $I_{\rm mfg}$  and  $I_{\rm out}$ , (Figure 6). This current is stored permanently and results from the copy of an input current  $I_{\rm in}$  by using a feedback loop. Thus, the stored charge can be read out as an analogue current from MFG<sub>2</sub>. Some important electrical characteristics of the cell are presented in Table 1.

The operation of the storage cell is explained in three stages as follows.

3.1. Initialization. The capacitor  $C_2$  is set to an initial potential of  $V_{\rm tun}=-25~{\rm V}$  and transistor M12 must be turned on in order to lead  $V_c$  to ground. This condition  $V_c=0~{\rm V}$  sets  $V_{\rm FG}=0~{\rm V}$  through capacitor  $C_1$ . As a result,  $V_{\rm ox}=-25~{\rm V}$  enabling F-N tunneling current through polyl-poly2 capacitor  $C_2$ . Consequently, electrons are injected to the FG causing a potential drop of  $V_{\rm FG}$  relative to ground, increasing the current  $I_{\rm mfg}$  from MFG $_1$  transistor. This memory has been verified to store analogue current values in the range of 30  $\mu$ A <  $I_{\rm out}<70~\mu$ A; therefore, the initial current condition must

TABLE 1: Electrical values for the memory cell.

| Electrical parameter | Value                                       |

|----------------------|---------------------------------------------|

| $V_{ m DDI}$         | 3.3 V                                       |

| $V_{ m DD2}$         | 8 V                                         |

| $C_1$                | 1 pF                                        |

| $C_2$                | 3 fF                                        |

| $C_{ m par}$         | 360 fF                                      |

| $R_1, R_2$           | $1E99\Omega$                                |

| $MFG_{1,2}$          | $6 \mu\mathrm{m}/3 \mu\mathrm{m}$           |

| M1, M2, M4, M5       | $6 \mu\mathrm{m}/3 \mu\mathrm{m}$           |

| M3                   | 30 μm/1.5 μm                                |

| M6, M9               | $12 \mu\mathrm{m}/6 \mu\mathrm{m}$          |

| M7, M8               | $30  \mu \text{m}/6  \mu \text{m}$          |

| M10                  | $12 \mu\mathrm{m}/6 \mu$                    |

| M11                  | $60  \mu \text{m} / 6  \mu \text{m}$        |

| M12                  | $100  \mu \mathrm{m} / 1.5  \mu \mathrm{m}$ |

| $I_{ m bias}$        | $50 \mu\mathrm{A}$                          |

| $V_{ m ref}$         | 1.5 V                                       |

| $V_{b1}$             | 3.3 V                                       |

| $V_{ m read}$        | 0-3.3 V                                     |

fulfill  $I_{\rm mfg}$  > 70  $\mu$ A for a proper operation of the cell feedback loop.

3.2. Programming. The programming stage starts setting an input current value  $I_{\rm in}$ , which will be stored in the cell permanently. A potential of  $V_{\rm tun}$ = 25 V must be also established on  $C_2$  and transistor M12 must be turned off. The current to be stored is introduced by the current source  $I_{\rm in}$ , where transistors M1, M2, and M3 act as a cascode current mirror with high output impedance at node "x." Thus, node "x" will have high gain and since  $I_{\rm mfg} > I_{\rm in}$ , the potential in this node will be close to  $V_{\rm DD1}$ . The comparator allows even a higher gain from node "x" and was considered in order to reduce the error of  $I_{\rm out}/I_{\rm in}$ . Moreover, this comparator allows an adjustable reference through  $V_{\rm ref}$ . The push-pull inverter brings a rail-to-rail output from the comparator output; indeed, this inverter has a  $V_{\rm DD2}$  = 8 V whose output  $V_{\rm c}$  is induced to the FG through capacitor  $C_1$ .

Thus, when voltage at node "x" is close to  $V_{\rm DD1}$ , the inverter brings  $V_c=0~\rm V$  which sets the FG also to 0 V, as mentioned above. This voltage difference between  $V_{\rm tun}$  and  $V_{\rm FG}$  is greater than 24 V ( $V_{\rm ox}>24~\rm V$ ); then, electron tunneling is achieved, which extracts electrons from the FG causing an increase on  $V_{\rm FG}$ . As a result, the current  $I_{\rm mfg}$  is decreased. Consequently, potential  $V_{\rm FG}$  rises until node "x" reaches  $I_{\rm in} \approx I_{\rm mfg}$  by the use of the feedback loop. When  $I_{\rm in}$  is slightly greater than  $I_{\rm mfg}$ , the potential at node "x" drops to a value near ground; this causes a "high" output from the inverter,  $V_c=8~\rm V$ . This 8 V output of the circuit applied to  $C_1$  capacitor stops tunneling since now  $V_{\rm ox}<24~\rm V$ . This control loop makes this cell a novel design since only 8 V on-chip is necessary in order to stop tunneling with the feedback loop.

FIGURE 6: Analog current-mode memory cell.

Finally,  $I_{\rm mfg}$  current of MFG transistor will be equal to  $I_{\rm in}$  current, which is permanently stored by means of the stored charge in the FG.

3.3. Reading. Cell reading is performed under the following conditions:  $V_{\rm tun}=0\,{\rm V}$  and  $V_c=0\,{\rm V}$ . For this purpose, transistor M12 must be turned on in order to lead  $V_c$  to ground. The output current  $I_{\rm out}$  is a copy of  $I_{\rm mfg}$  and is obtained from the drain of transistor M4.

# 4. PSpice Simulations and Experimental Results

4.1. Macromodel for  $I_{tun}$  Electrical Simulation. Spice is a world standard program for electrical circuit simulation. A macromodel is a combination of Spice models used for a special purpose device. Since F-N tunneling current is not modeled in Spice, the F-N expression is implemented as a macromodel with the use of a voltage-controlled current source (VCCS); that is,

G1 1 2 VALUE =

$$\left\{190.1e - 9 * [V(1) - V(2)]^{2} \right.$$

$$\left. * EXP \left\{ \frac{-578.15}{[V(1) - V(2)]} \right\} \right\}$$

$$R1 1 2 1e99,$$

(10)

where "G" is associated with a voltage controlled current source and 1 and 2 are the nodes where the current source is connected. Node 1 represents external applied voltage  $V_{\rm tun}$  which is ground referenced and node 2 represents the  $V_{\rm FG}$ . The "VALUE" parameter allows the implementation of (9) including the injector area of  $C_2$ ; in this case  $A=1.8~\mu{\rm m} \times 1.8~\mu{\rm m}$  and distance  $d=38.4~{\rm nm}$ . Additionally, a resistor R1

is included with a high value in order to improve simulation convergence. The VCCS G1 and R1 are shown in dashed line in Figure 6.

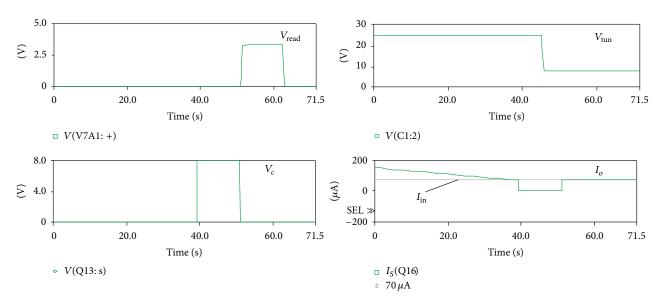

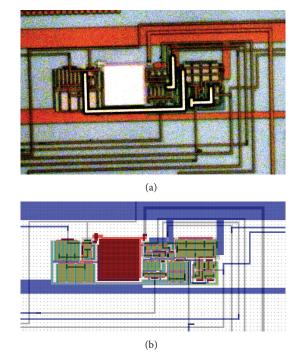

4.2. Spice Electrical Cell Simulation. An electrical cell simulation using PSpice is shown in Figure 7. The cell also includes resistor R2, which is used for improving convergence and helps the simulator to set the DC operation point at the floating gate. Furthermore, capacitor  $C_{\rm par}$  models the FGsubstrate parasitic capacitor. In this case this capacitor can be calculated using the layer capacitance parameters given by the foundry and the injector area, in this case, has a value of  $C_{\rm par}$ = 360 fF. When an input current  $I_{\rm in}$  = 70  $\mu$ A is established on the cell, the initial output current is  $I_{\rm mfg} = 160 \, \mu {\rm A}$  and after 40 s this output current drops to  $\sim$ 70  $\mu$ Å. At this point, V<sub>C</sub> rises to 8 V and F-N tunneling is stopped. Afterwards, at 50 s, the  $V_{\rm tun}$  is removed and transistor M14 is turned on; this enables the readout current,  $I_{\text{out}} = 70.1 \,\mu\text{A}$ . The cell worked properly at the range 70  $\mu$ A <  $I_{\rm out}$  < 30  $\mu$ A. The highest error, error =  $|I_{out} - I_{in}|$ , is obtained when current values are near  $30 \,\mu\text{A}$ . It is important to notice that although a deviation in (9) could be present, only the cell convergence time to reach  $I_{\rm in} \approx I_{\rm mfg}$  would be affected by several seconds. A microphotograph of a chip is shown in Figure 8.

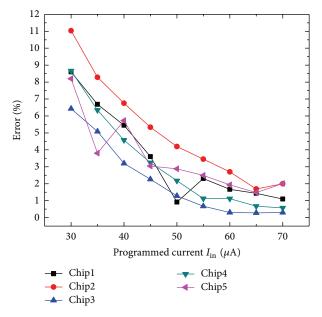

The measured relative error percentages for several programming input current values are shown in Figure 9. The error calculation was considered using

error % =

$$\left| \frac{I_{\text{out}} - I_{\text{in}}}{I_{\text{in}}} \right| \times 100.$$

(11)

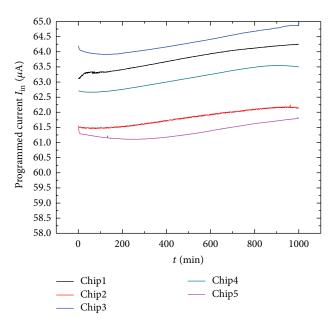

From experimental data, the error is less than 5% in the range  $70~\mu\text{A} < I_{\text{out}} < 50~\mu\text{A}$ . Therefore this is considered the working range of the cell. In Figure 10, the plot shows a set of five cells supplying currents between  $I_{\text{out}} = 60~\mu\text{A}$  to  $65~\mu\text{A}$

Figure 7: Transient simulation of the analog memory cell for a 70  $\mu$ A input current.

FIGURE 8: Memory cell microphotograph and layout.

over a long period of time. The charge retention of the floating gate has been confirmed by the measurements of the cells over 1000 minutes. In submicron technologies, gate leakage is well known [9]; thus, a constant measurement of the cell could show a change in the charge trend. Nevertheless, a further statistical analysis of this situation should be considered for periods  $\gg$  1000 min, since this could give important information about the usefulness of the cell, that is, reliability and refreshing cycles.

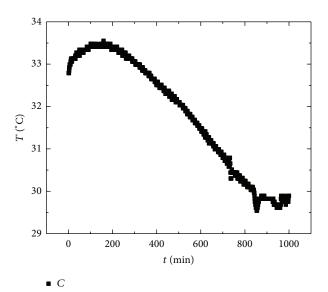

In Figure 11, the graph shows ambient temperature measurement at the same time span. A correlational fluctuation

Figure 9: Error percentage from output current  $I_{\rm out}$  for several input current values  $I_{\rm in}.$

of the current value is observed and caused by the ambient temperature. Considering  $\Delta I_{\rm out}$  from Figure 10 and  $\Delta T$  from Figure 11, the storage cell presents a temperature dependence of  $-221\,{\rm nA/^\circ}{\rm C}.$  Therefore, the stored charge onto the floating gate does not present a significant change at the same period of time.

#### 5. Conclusions

In this work, a novel nonvolatile current-mode analog memory cell architecture is presented. A control loop is used with only 8V to stop F-N tunneling. This is a new approach that allows the use of standard circuitry internally in order

Figure 10: Output current  $I_{\rm out}$  in a time span of 1000 minutes.

Figure 11: Ambient temperature variation.

to program nonvolatile analog cells on chip. Experimental results show that the cell presents a useful range of values with a maximum error of 5%. The functionality of the cell was analyzed through a long period of time (1000 min) and also temperature performance was analyzed.

#### **Conflict of Interests**

The authors declare that there is no conflict of interests regarding the publication of this paper.

#### References

- [1] B. A. Minch, P. Hasler, and C. Diorio, "Synthesis of multipleinput translinear element networks," in *Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS '99)*, vol. 2, Orlando, Fla, USA, June 1999.

- [2] M. Lenzlinger and E. H. Snow, "Fowler-Nordheim tunneling into thermally grown SiO2," *IEEE Transactions on Electron Devices*, vol. 15, no. 9, 1968.

- [3] R. G. Benson and D. A. Kerns, "UV-activated conductances allow for multiple time scale learning," *IEEE Transactions on Neural Networks*, vol. 4, no. 3, pp. 434–440, 1993.

- [4] O. Fujita and Y. Amemiya, "Floating-gate analog memory device for neural networks," *IEEE Transactions on Electron Devices*, vol. 40, no. 11, pp. 2029–2035, 1993.

- [5] R. R. Harrison, J. A. Bragg, P. Hasler, B. A. Minch, and S. P. Deweerth, "A CMOS programmable analog memory-cell array using floating-gate circuits," *IEEE Transactions on Circuits and Systems II*, vol. 48, no. 1, pp. 4–11, 2001.

- [6] M. E. Figueroa Toro, Adaptive signal processing and correlational learning in mixed-signal VLSI [Ph.D. dissertation], University of Washington, 2005.

- [7] C. Diorio, D. Hsu, and M. Figueroa, "Adaptive CMOS: from biological inspiration to systems-on-a-chip," *Proceedings of the IEEE*, vol. 90, no. 3, pp. 345–357, 2002.

- [8] A. K. Sharma, Advanced Semiconductor Memories, Architectures, Designs and Applications, John Wiley & Sons, 1st edition, 2003.

- [9] P. Hafliger and H. K. O. Berge, "Exploiting gate leakage in deep-submicrometer CMOS for input offset adaptation," *IEEE Transactions on Circuits and Systems II*, vol. 54, no. 2, pp. 127– 130, 2007.

Submit your manuscripts at http://www.hindawi.com